ФЭА / АИТ / ДЕШИФРАТОРЫ И ШИФРАТОРЫ

(автор - student, добавлено - 19-06-2014, 13:54)

ДЕШИФРАТОРЫ И ШИФРАТОРЫ

Общие сведения Дешифраторы и шифраторы по существу принадлежат к числу преобразователей кодов. С понятием шифрации связано представление о сжатии данных, с понятием дешифрации - обратное преобразование. Комбинационная схема, преобразующая поступающий на входы код в сигнал только на одном из ее выходов, называется дешифратором. В условных обозначениях дешифраторов и шифраторов используются буквы DC и CD (от слов decoder и coder соответственно). Если количество двоичных разрядов дешифруемого кода обозначить через n, то число выходов дешифратора должно быть 2n.Так как с помощью n-разрядного двоичного кода можно отобразить 2n кодовых комбинаций, число выходов полного дешифратора равна 2n. Таким образом, дешифратор содержит число выходов, равное числу комбинаций входных переменных, например, если число входов равно 3, то число выходов (Nвых) равно 23=8. Если часть входных наборов не используется, то дешифратор называют неполным и у него Nвых<2n. В ЭВМ с помощью дешифраторов осуществляется выборка необходимых ячеек запоминающих устройств, расшифровка кодов операций с выдачей соответствующих управляющих сигналов и т.д. Если входные переменные представить как двоичную систему запись чисел, то логическая единица формируется в том выходе, номер которого соответствует десятичной записи того же числа. Например, A = 1, B = 0, C = 0, D = 1, число 1001 в двоичном коде. В десятичной коде это число соответствует 9, т.е. при данной комбинации входных переменных F9 = 1. Дешифраторы широко используются в качестве преобразователей двоичного кода в десятичный, а также во многих других устройствах.

Исследование работы дешифратора

Цель работы Ознакомление с принципом работы дешифраторов и шифраторов; исследование влияния управляющих сигналов на их работу. Краткие сведения из теории Одноступенчатый дешифратор (линейный) - наиболее быстродействующий, но его реализация при значительной разрядности входного слова затруднена, поскольку требует применения логических элементов с большим числом входов (равным n+1 для вариантов со стробированием по выходу) и сопровождается большой нагрузкой на источники входных сигналов. Обычно одноступенчатыми выполняются дешифраторы на небольшое число входов, определяемое возможностями элементов применяемой серии микросхем. Появление малоразрядных дешифраторов (пирамидальный и матричный) в виде схем средней степени интеграции (СИС) поставило вопрос о применении их как средств построения дешифраторов большей разрядности, что дает существенную экономию аппаратурных затрат. Любой нужный дешифратор может быть построен по пирамидальной структуре. Причем входное слово делится на поля, разрядность которых соответствует числу входов имеющихся СИС дешифраторов, а затем из СИС строится пирамидальная структура, составляющая совокупность линейных дешифраторов. Матричные дешифраторы формируются на основе простых линейных дешифраторов меньшей размерности, т.е. строятся в виде матрицы. Таблица 1 Таблица истинности дешифратора

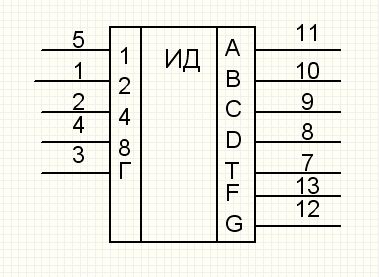

КР514ИД2

Микросхема представляет собой дешифратор для семисегментного полупроводникового индикатора с разъединенными катодами сегментов. Предназначен для работы в электронной аппаратуре в качестве дешифратора логических сигналов из двоичного кода 8-4-2-1 в семисегментный код для питания цифровых полупроводниковых индикаторов.

Условное обозначение КР514ИД2 Назначение выводов: 1,2,3,4,5 – входы; 6 – общий; 8,9,10,11,12,13 – выходы; 14 – напряжение питания.

Электрические параметры.

Похожие статьи:

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||